## MACH™ 1 and MACH 2 Families

# High Density EE CMOS Programmable Logic

Final:

MACH110 Com'l MACH210 Com'l Q2 1991 Data Book

Preliminary:

MACH110 Mil

MACH120 Com'l

MACH130 Com'l, Mil

MACH210 Mil

MACH230 Com'l, Mil

Advance Information

MACH220 Com'l

#### © 1991 Advanced Micro Devices, Inc.

Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

This publication neither states nor implies any warranty of any kind, including but not limited to implied warrants of merchantability or fitness for a particular application. AMD assumes no responsibility for the use of any circuitry other than the circuitry in an AMD product.

The information in this publication is believed to be accurate in all respects at the time of publication, but is subject to change without notice. AMD assumes no responsibility for any errors or omissions, and disclaims responsibility for any consequences resulting from the use of the information included herein. Additionally, AMD assumes no responsibility for the functioning of undescribed features or parameters.

#### **Trademarks**

PAL and PALASM are registered trademarks of Advanced Micro Devices, Inc.

LabPro and MACH are trademarks of Advanced Micro Devices, Inc.

ABEL, SmartPart, and PLDtest are trademarks of Data I/O Corporation.

LogicPak and UniSite are trademarks of Data I/O Corporation.

OrCAD/SDT, OrCAD/VST, and OrCAD/PLD are trademarks of OrCAD Systems Corporation.

PGADesigner is a trademark, of Minc Inc.

SmartModel is a registered trademark of Logic Automation.

CUPL is a trademark of Logical Devices, Inc.

LOG/iC is a trademark of ISDATA GmbH.

ATGEN is a trademark of Acugen Software, Inc.

Cover plane image courtesy of NASA.

If you have always wanted higher-density EE CMOS PAL® devices, with no penalty in speed or cost per function, this booklet will help you a lot!

We have taken our high-volume 0.8-micron EE CMOS PAL device process and applied it to a new family of 44-, 68-, and 84-pin 15-ns PLDs aimed at letting you meet your designs' speed and real estate targets.

In just a few short years, AMD has become a force in CMOS PLDs, building on our #1 spot in bipolar. With the new benefits that our breakthrough architecture CMOS family brings you, we continue moving towards the #1 spot in CMOS too.

By providing a breadth of architectures and technologies, we hope to make it easier for you to get your new product to market quickly enough to win in this ultra-competitive world.

Andy Robin

Director of Marketing Programmable Logic

Andrew D. Polici

#### INTRODUCTION

This book introduces you to the new MACH 1 and MACH 2 families of programmable logic from Advanced Micro Devices. These devices provide programmable logic capabilities from around 900 gates to 3600 gates. Included in this book are a general discussion, the MACH110 and MACH210 final data sheets, the preliminary data sheets for the next three family members, and advance information on the final devices.

The general discussion deals with those issues that affect the entire device family, including a brief discussion of the PALASM® software used to configure the devices. Because of the common architecture, most of the understanding of the device can come from a look at the families as a whole. Individual devices differ only in number of resources.

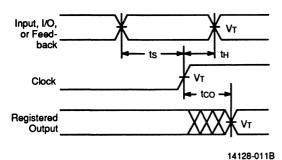

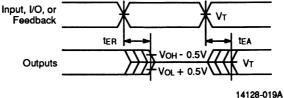

The data sheets discuss items that are specific to the first four devices: the MACH110, MACH120, MACH130, and MACH210. They contain the basic DC and switching specifications. Other general specifications, such as switching waveforms and endurance, follow the data sheets, since they are the same for all devices.

Finally, an advance information sheet provides a look at the last member of the MACH 2 family: the MACH220.

The order in which the products appear in the databook has been changed in this edition. From this edition on, all devices will appear in numerical order according to the device name, regardless of release status. This should make it easier for you to find devices in future editions.

## **TABLE OF CONTENTS**

| IACH Device Family Description    |   |

|-----------------------------------|---|

| ACH 1 Family                      |   |

| IACH110-15/20                     |   |

| IACH120-15/20                     |   |

| MACH130-15/20                     |   |

| IACH 2 Family                     |   |

| IACH210-15/20                     |   |

| IACH220-15/20                     |   |

| IACH230-15/20                     |   |

| General Information               |   |

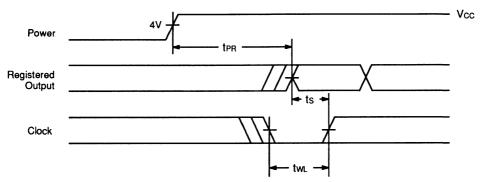

| witching Waveforms                |   |

| ndurance Characteristics          |   |

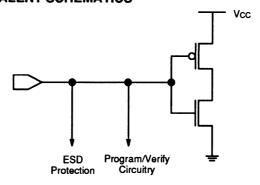

| nput/Output Equivalent Schematics |   |

| ower-Up Reset                     |   |

| pproved Programmers               |   |

| rogrammer Socket Adapters         |   |

| evelopment Systems                | • |

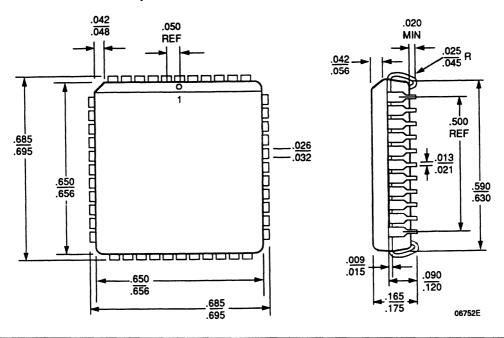

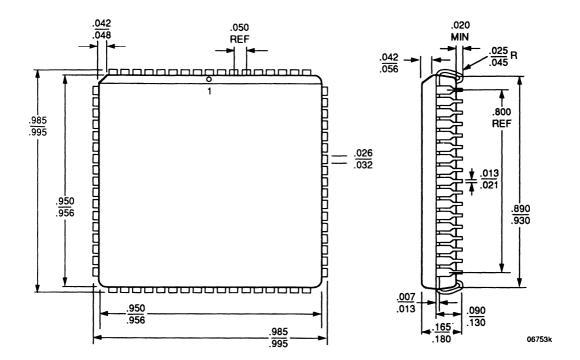

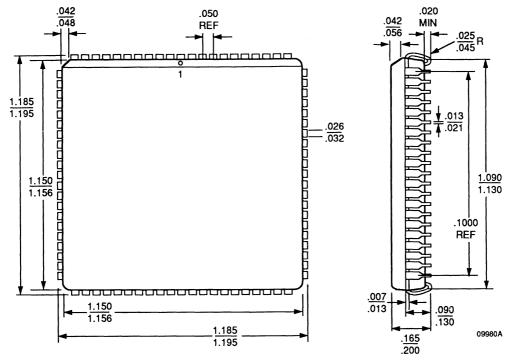

| hysical Dimensions                |   |

## **MACH Device Family**

## **High-Density EE CMOS Programmable Logic**

#### DISTINCTIVE CHARACTERISTICS

- High-performance, high-density, electrically-erasable CMOS PLD families

- 900 to 3600 gate equivalents

- 44 to 84 pins in cost-effective PLCC and CQFP packages

- 32 to 128 macrocells

- 0.8-µm CMOS provides predictable design-independent high speeds

- Commercial 15-ns/20-ns tpD, 50-MHz/40-MHz fmax

- Military 20-ns tpd, 40-MHz fmax

- PAL blocks connected by switch matrix

- Provides optimized global connectivity

- Switch matrix integrates blocks into uniform device

#### **■** Configurable macrocells

- Programmable polarity

- Registered or combinatorial

- Internal and I/O feedback

- D-type or T-type flip-flops

- Choice of clocks for each flip-flop

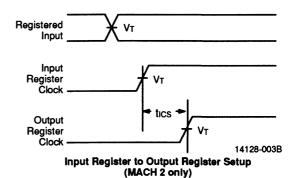

- Input registers for MACH 2 family

## Supported by popular industry-standard design software

- Schematic capture and text entry

- Compilation and JEDEC file generation

- Design simulation

- Logic and timing models

- Programmable on standard programmable logic device programmers

#### **PRODUCT SELECTOR GUIDE**

| Device        | Pins | Macrocells | Gate<br>Equivalents | Max<br>Inputs | Max<br>Outputs | Max<br>Flip-Flops | Speed<br>(ns) |

|---------------|------|------------|---------------------|---------------|----------------|-------------------|---------------|

| MACH 1 Family |      |            |                     |               |                |                   |               |

| MACH110       | 44   | 32         | 900                 | 38            | 32             | 32                | 15, 20        |

| MACH120       | 68   | 48         | 1200                | 56            | 48             | 48                | 15, 20        |

| MACH130       | 84   | 64         | 1800                | 70            | 64             | 64                | 15, 20        |

| MACH 2 Family |      |            |                     |               |                |                   |               |

| MACH210       | 44   | 64         | 1800                | 38            | 32             | 64                | 15, 20        |

| MACH220       | 68   | 96         | 2400                | 56            | 48             | 96                | 15, 20        |

| MACH230       | 84   | 128        | 3600                | 70            | 64             | 128               | 15, 20        |

### **GENERAL DESCRIPTION**

The MACH (Macro Array CMOS High-density) family provides a new way to implement large logic designs in a programmable logic device. AMD has combined an innovative architecture with advanced CMOS technology to offer a device with several times the logic capability of the industry's most popular existing PAL device solutions at comparable speed and cost.

Their unique architecture makes these devices ideal for replacing large amounts of TTL logic. They are the first devices to provide such increased functionality without forcing the designer to sacrifice speed and cost.

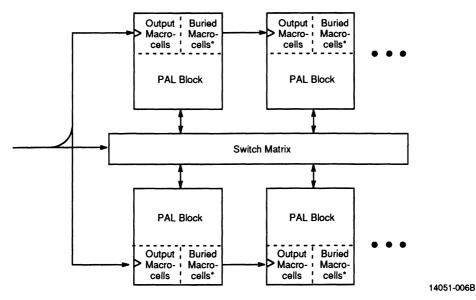

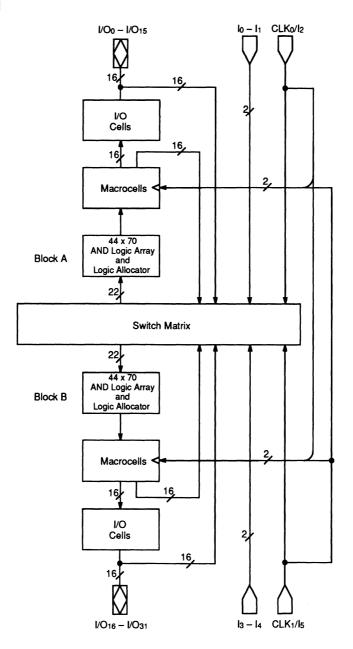

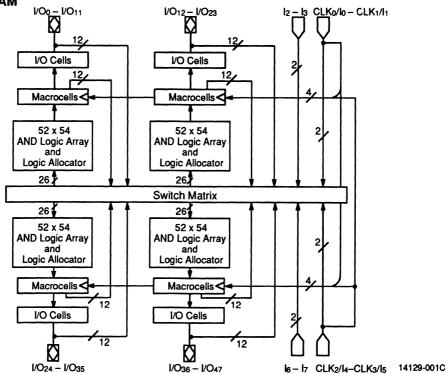

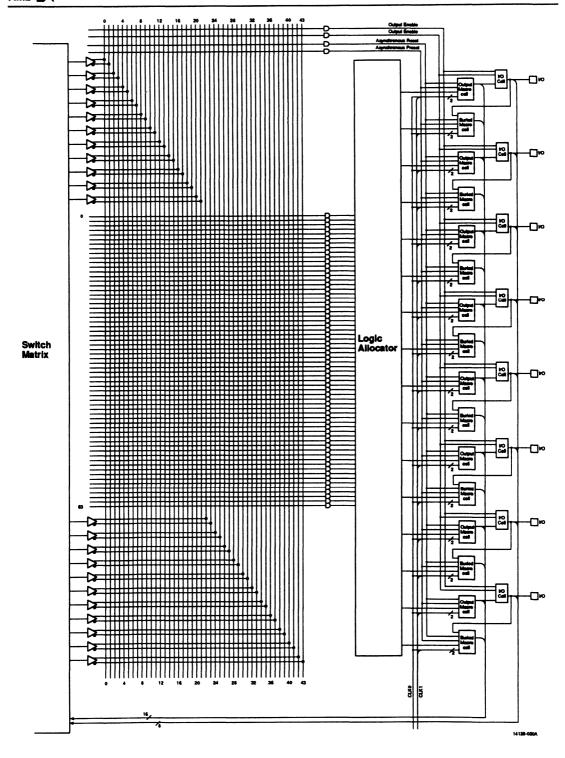

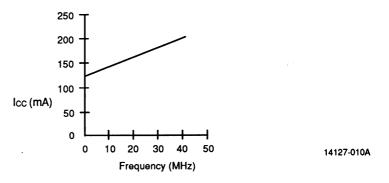

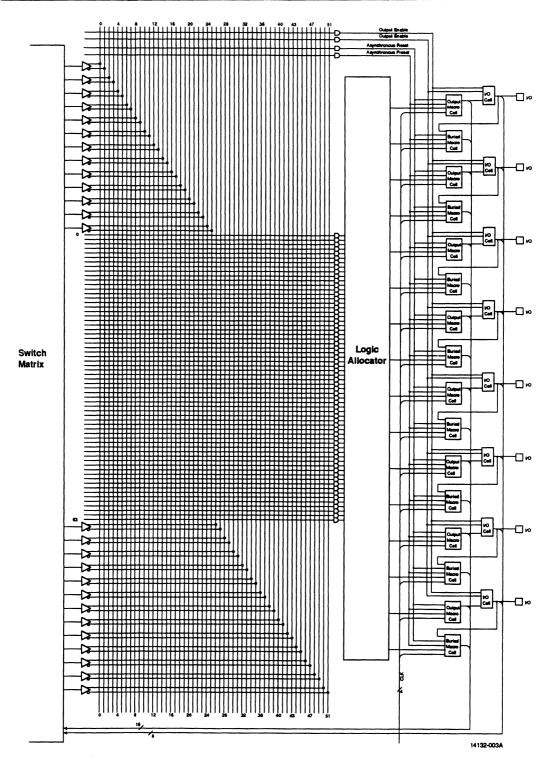

The MACH devices consist of PAL blocks interconnected by a programmable switch matrix (figure 1). Designs that consist of several interconnected functional

modules can be efficiently implemented by placing the modules into the PAL blocks. Designs that are not as modular can still be implemented since the switch matrix provides a high level of connectivity between the PAL blocks. This internal arrangement of resources is managed automatically by the design software, so that the designer does not have to be concerned with the logic implementation details.

The MACH family is supported by AMD's PALASM software development system. This software runs on PC/AT-compatible and 386-based systems. The package provides low-cost CAD capability while easing all the important phases of the designer's task: design entry, implementation, verification, programming, and

Publication# 14051 Rev. C Amendment/0 Issue Date: April 1991

testing. The MACH devices can be programmed on conventional PAL device programmers with appropriate personality and socket adapter modules.

The MACH 1 and MACH 2 families are manufactured using AMD's state-of-the-art advanced CMOS electri-

cally-erasable process for high performance and logic density. The CMOS EE technology provides 100% testability, thus reducing the designer's prototype development costs.

<sup>\*</sup> Buried macrocell available on MACH 2 devices only.

Figure 1. General MACH Device Block Diagram

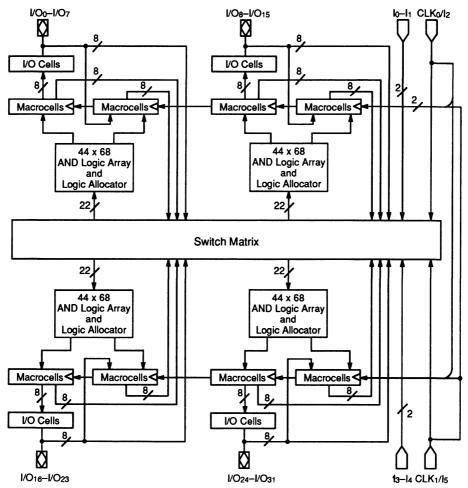

#### THE MACH 1 AND MACH 2 FAMILIES

The MACH 1 and MACH 2 families each consist of several members. The first three members of each family are discussed in this book. The items that differentiate the members of the family are the number of pins, the number of macrocells, the amount of interconnect, and the number of clocks. The MACH 1 family has output macrocells; the MACH 2 family has output and buried macrocells. In all other respects, the two families are the same.

This provides a convenient way of migrating designs up or down with little difficulty. Because there is a choice of I/O-pin-to-macrocell ratio, the designer can choose a device that suits both his internal logic needs and his I/O needs. In the future, the software will also be able to provide automatic partitioning and device selection to make the design process device-independent.

The first devices range in pin count from 44 to 84, and in number of macrocells from 32 to 128. All devices are provided in cost-effective PLCC packages; military versions are available in CQFP packages.

#### Design Methodology

An important aspect of the MACH family is the fact that design tools are widely available both from AMD and

from third-party software vendors. AMD provides PALASM software as a lower cost baseline tool set and works with tools vendors to ensure broad MACH device support. This allows designers to do MACH device designs using the same tools that they would use to do PAL device designs, whether PALASM software or any of the other popular PAL device design packages.

Design entry is the same as that used for PAL devices, including the capability of using schematic capture for design packages such as PALASM 4 software. The basic logic processing steps are also the same steps that are needed to process and minimize logic for any PAL device. Simulation is available for verifying the correct behavior of the device. Functional (unit-delay) simulation of MACH devices is supported in all the packages, and other options for simulating the timing and board-level behavior of the MACH devices are available as options. In all cases, the desired end result is a JEDEC file that can be downloaded to a programmer for device configuration.

The MACH design methodology differs from that of a PAL device somewhat due to the automatic design fitting procedure that the software performs. Designs written by logic designers—whether by schematic capture.

state machine equations, or Boolean equations—are partitioned and placed into the PAL blocks of the MACH device. While this procedure is handled automatically by the software, the software can also accept manual direction based upon the user's working knowledge of the design. The overall device utilization provided by the fitter will vary from design to design, but 70% utilization is typical.

In general, letting the software decide the best fit and pin placement automatically for the first iteration of the design provides the best chance of fitting. It can also be useful to implement large designs incrementally, starting with low device utilization and building up by adding logic until the device is full. This generally means that designs are done without any specific pinout assignments, with the final pinout decided by the software. However, it is possible to pre-place signals. If done carefully, this can help the software fit difficult designs; if not done carefully, it may make it harder for the design to fit. Guidelines on specifying the initial pinout are provided in the MACH user's manual.

Once an initial design fits, there may be subsequent changes to the design. This is important if board layout has already started based on the original pinout. If changes are too dramatic, then it may be necessary to refit the design, potentially resulting in a new pinout. The stability of the design and the expected extent of any changes should therefore be considered before committing the design to layout. Careful designs that target about 70% utilization will make future changes much easier. Hints on designing for change can be found in the software documentation.

In all cases, the way the design is partitioned and placed into the MACH device by the software does not affect the performance of the design. With designs that do not fit, it is possible to make some performance tradeoffs to aid in fitting (for example, by optimizing the flip-flop type or using multi-level logic), but those tradeoffs must be specifically requested, and any additional delays are entirely predictable.

#### **Functional Description**

The fundamental architecture of the MACH devices consists of several PAL blocks interconnected by a switch matrix. The switch matrix allows communication between PAL blocks, and routes inputs to the PAL blocks. Together the PAL blocks and switch matrix allow the logic designer to create large designs in a single device instead of multiple devices.

Most pins are I/O pins that can be used as inputs, outputs, or bidirectional pins. There are some dedicated input pins, but all macrocells have internal feedback, allowing the pin to be used as an input if the macrocell signal is not needed externally.

The key to being able to make effective use of these devices lies in the interconnect schemes used. Because of the use of programmable interconnections, the product-term arrays have been decoupled from the switch matrix, the macrocells, and the I/O pins. This provides

much greater flexibility, and allows designs to be placed and routed efficiently and quickly.

The internal architecture is such that all signals incur the same delays, regardless of routing. This means that the performance of a design is design-independent, and is known before the design is even begun.

#### The PAL Blocks

The PAL blocks can be viewed as independent PAL devices on the chip. This provides for logic functions that need the complete interconnect that a PAL device provides. The PAL blocks communicate with each other only through the switch matrix.

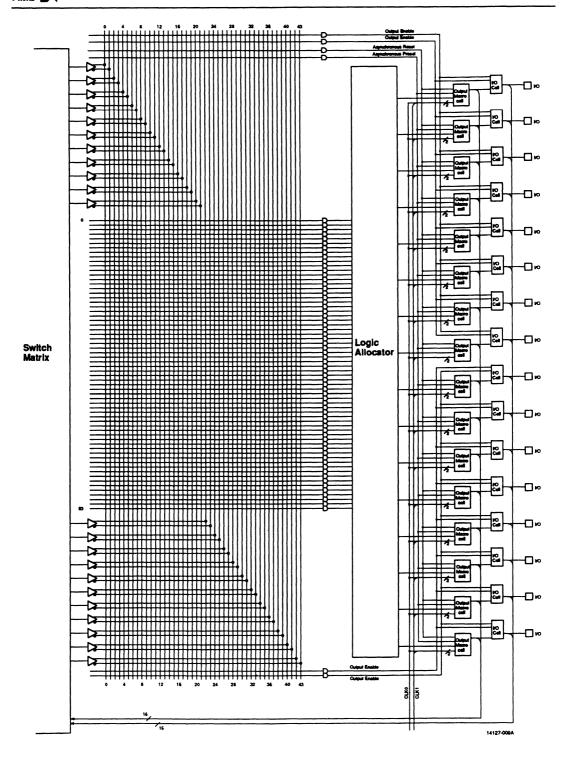

Each PAL block contains a product-term array, a logic allocator, macrocells, and I/O cells. The product-term array generates the basic logic, although the number of product terms per macrocell is variable. The logic allocator distributes the product terms to the macrocells. This allows the distribution of product terms as required by the design. The macrocell configures the signal, and the I/O cell delivers the final signal to the output pin.

Each PAL block additionally contains an asynchronous reset product term and an asynchronous preset product term. This allows the flip-flops within a single PAL block to be initialized as a bank. There are also several three-state product terms that provide three-state control to the I/O cells.

#### The Switch Matrix

The switch matrix takes all dedicated inputs, I/O feedback signals, and buried feedback signals and routes them as needed to the various PAL blocks. Feedback signals that only return to the same PAL block still go through the switch matrix. This provides a way for the PAL blocks to communicate with each other with consistent, predictable delays. It is the switch matrix which makes the MACH devices more than just multiple PAL devices on a single chip.

For designs that consist of smaller functional units that are connected together, the PAL blocks provide the routing software with local full connectivity for each unit, connected by the switch matrix. For designs that are larger in scope, the switch matrix allows the designer to think of the device not as a collection of blocks, but as a single programmable device; the software partitions the design into the PAL blocks through the switch matrix so that the designer does not have to be concerned with the internal organization.

#### The Product-Term Array

The product-term array consists of a number of product terms that form the basis of the logic being implemented. The inputs to the AND gates come from the switch matrix, and are provided in both true and complement forms for efficient logic implementation.

Because the number of product terms allocated to each macrocell is not fixed, the full sum of products is not realized in the array. The product terms drive the logic

allocator, which allocates the product terms to the appropriate macrocells.

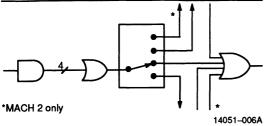

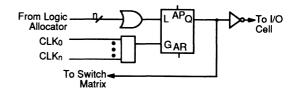

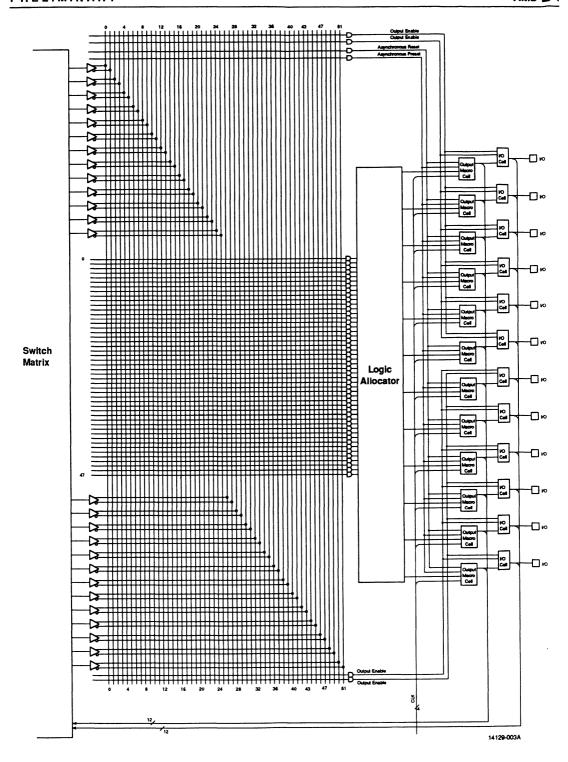

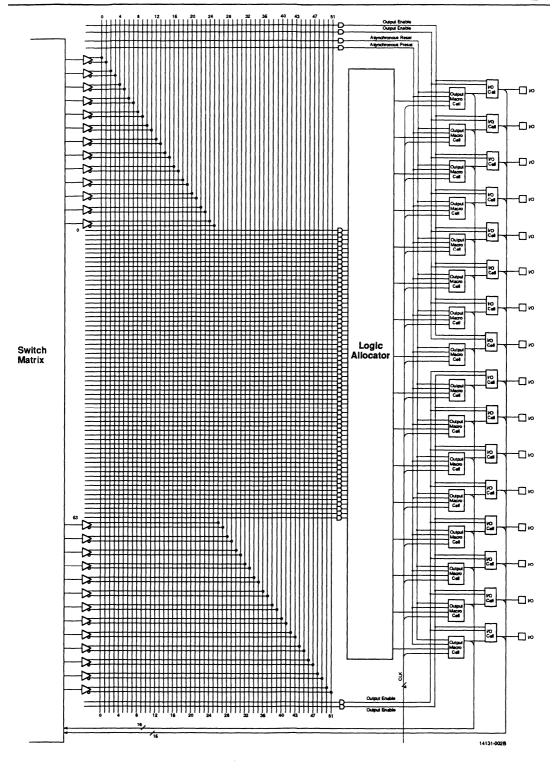

Figure 2. The Logic Allocator

### The Logic Allocator

The logic allocator (figure 2) is a block within which different product terms are allocated to the appropriate macrocells in blocks of four product terms. The availability and distribution of product terms is automatically considered by the software as it places and routes functions within the PAL block. The product-term distribution has been designed to provide high utilization of product terms. Complex functions using many product terms are possible, yet fewer product terms will be left unused—or wasted—when the design is complete.

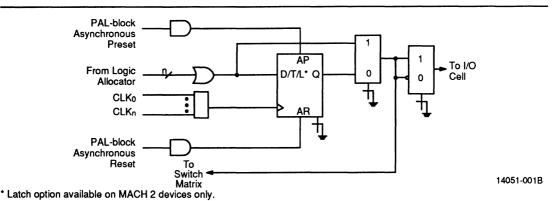

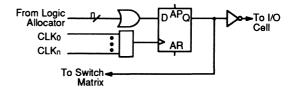

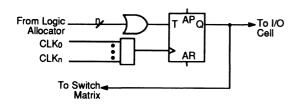

#### The Macrocell

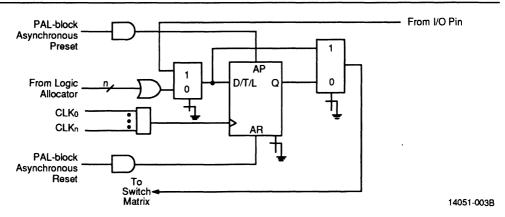

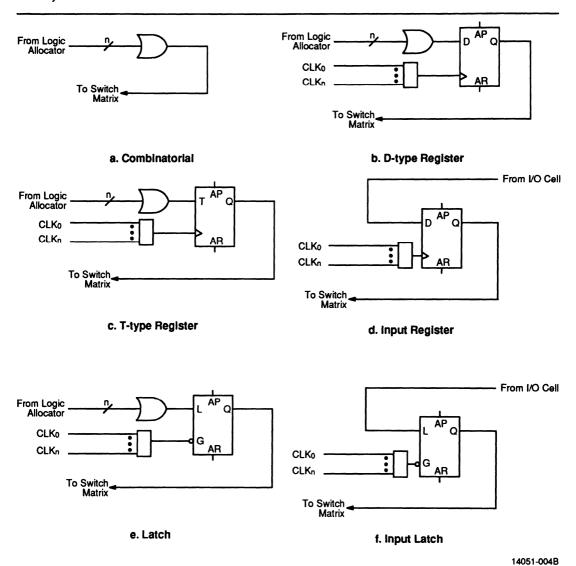

There are two fundamental types of macrocell: the output macrocell and the buried macrocell. The buried macrocell is only found in MACH 2 devices. The use of buried macrocells effectively doubles the number of macrocells available without increasing the pin count.

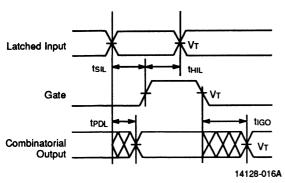

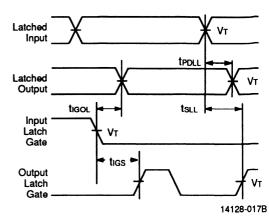

Both macrocell types can generate registered or combinatorial outputs. For the MACH 2 series, a transparent-low latched configuration is provided. If used, the register can be configured as a T-type or a D-type flip-flop. Programmable polarity (for output macrocells) and the T-type flip-flop both give the software a way to minimize the number of product terms needed. These choices can be made automatically by the software when it fits the design into the device.

The output macrocell (figure 3) sends its output back to the switch matrix, via internal feedback, and to the I/O cell. The feedback is always available regardless of the configuration of the I/O cell. This allows for buried combinatorial or registered functions, freeing up the I/O pins for use as inputs if not needed as outputs. The basic output macrocell configurations are shown in figure 4.

Figure 3. Output Macrocell

### a. Combinatorial, Active High

### b. Combinatorial, Active Low

#### c. D-type Register, Active High

d. D-type Register, Active Low

#### e. T-type Register, Active High

f. T-type Register, Active Low

g. Latch, Active High (MACH 2 only)

h. Latch, Active Low (MACH 2 only)

14051-002B

Figure 4. Output Macrocell Configurations

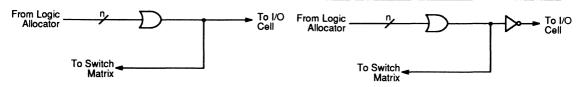

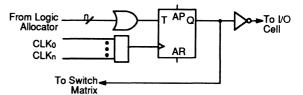

The buried macrocell (figure 4) does not send its output to an I/O cell. The output of a buried macrocell is provided only as an internal feedback signal which feeds the switch matrix. This allows the designer to generate additional logic without requiring additional pins.

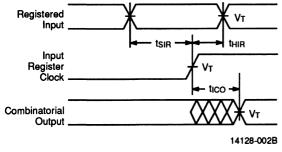

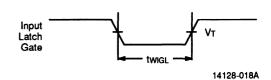

In addition to the capabilities of the output macrocell, the buried macrocell allows the use of registered or latched inputs. The input register is a D-type flip-flop; the input latch is a transparent-low D-type latch. Once configured as a registered or latched input, the buried macrocell cannot generate logic from the product-term array. The basic buried macrocell configurations are shown in figure 5.

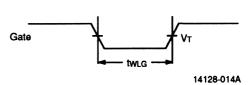

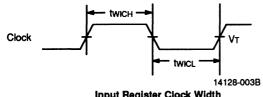

The flip-flops in either macrocell type can be clocked by one of several clock pins. Registers are clocked on the rising edge of the clock input. Latches hold their data when the gate input is HIGH. Clock pins are also available as inputs, although care must be taken when a signal acts as both clock and input to the same device. All flip-flops have asynchronous reset and preset. This is controlled by the common product terms that control all flip-flops within a PAL block. For a single PAL block, all flip-flops, whether in an output or a buried macrocell, are initialized together.

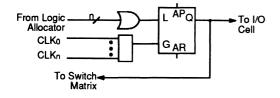

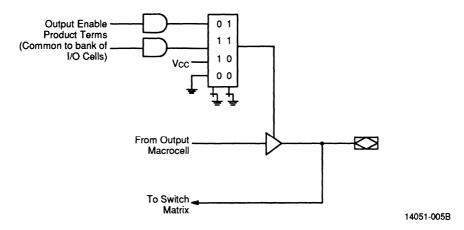

#### The I/O Cell

The I/O cell (figure 6) provides a three-state output buffer. The three-state buffer can be left permanently enabled, for use only as an output; permanently disabled, for use as an input; or it can be controlled by one of two product terms, for bidirectional signals and bus connections. The two product terms provided are common to a bank of I/O cells.

#### Register Preload

All registers on the MACH devices can be preloaded from the I/O pins to facilitate functional testing of complex state machine designs. This feature allows direct loading of arbitrary states, making it unnecessary to cycle through long test vector sequences to reach a desired state. In addition, transitions from illegal states can be verified by loading illegal states and observing proper recovery.

#### Observability

In addition to the control offered by preload, testing requires observability of the internal state of the device following a sequence of vectors. The MACH devices offer an observability feature that allows the user to send hidden buried register values to observable output pins.

For macrocells that are configured as combinatorial, the observability function suppresses the selection of the combinatorial output by forcing the macrocell output multiplexer into registered output mode. The observability function allows observation of the associated registers by overriding the output enable control and enabling the output buffer.

### **Power-up Reset**

All flip-flops power-up to a logic LOW for predictable system initialization. The actual values of the outputs of the MACH devices will depend on the configuration of the macrocell. The  $V_{\rm CC}$  rise must be monotonic and the reset delay time is 10  $\mu$ s maximum.

Figure 5. Buried Macrocell (MACH 2 only)

#### **Security Bit**

A security bit is provided on the MACH devices as a deterrent to unauthorized copying of the array configuration patterns. Once programmed, this bit defeats readback of the programmed pattern by a device programmer, securing proprietary designs from competitors. Programming and verification are also defeated by the security bit, but test vectors containing preload can be used independently of the security bit. The bit can only be erased in conjunction with the array during an erase cycle.

#### **Programming and Erasing**

The MACH devices can be programmed on standard logic programmers. They may also be erased to reprogram a previously configured device with a new program. Erasure is automatically performed by the programming hardware. No special erase operation is required.

Figure 6. Buried Macrocell Configurations (MACH 2 only)

### **Quality and Testability**

The MACH devices offer a very high level of built-in quality. The fact that the device is erasable allows direct verification of all AC and DC parameters. In addition, this verifies complete programmability and functionality of the device to provide the highest programming yields and post-programming functional yields in the industry.

### **Technology**

The MACH devices are fabricated with AMD's advanced electrically-erasable floating-gate 0.8-µm

CMOS technology. This provides the devices with performance and power consumption that are unmatched in the industry. The floating gate cells rely on Fowler-Nordheim tunneling to charge the gate, and have long proven their endurance and reliability. 20-year data retention is provided over operating conditions when devices are programmed on approved programmers.

The substrate of these devices is grounded, providing for a more efficient circuit. In addition, this provides substrate clamp diodes at all inputs, making them more immune to noisy input signals.

Figure 7. I/O Cell

## MACH110-15/20

## **High-Density EE CMOS Programmable Logic**

## Advanced Micro Devices

#### **DISTINCTIVE CHARACTERISTICS**

- **44** Pins

- 32 Macrocelis

- 15 ns tpD Commercial 20 ns tpD Military

- 50 MHz f<sub>MAX</sub> Commercial 40 MHz f<sub>MAX</sub> Military

- 38 Inputs

- 32 Outputs

- 32 Flip-Flops

- 2 "PAL22V16" Blocks

- Pin-compatible with MACH210

#### **GENERAL DESCRIPTION**

The MACH110 is a member of AMD's high-performance EE CMOS MACH 1 family. This device has approximately three times the logic macrocell capability of the popular PAL22V10 at an equal speed with a lower cost per macrocell.

The MACH110 consists of two PAL blocks interconnected by a programmable switch matrix. The two PAL blocks are essentially "PAL22V16" structures complete with product-term arrays and programmable macrocells. The switch matrix connects the PAL blocks to each other and to all input pins, providing a high degree

of connectivity between the fully-connected PAL blocks. This allows designs to be placed and routed efficiently.

The MACH110 macrocell provides either registered or combinatorial outputs with programmable polarity. If a registered configuration is chosen, the register can be configured as D-type or T-type to help reduce the number of product terms. The register type decision can be made by the designer or by the software. All macrocells can be connected to an I/O cell. If a buried macrocell is desired, the internal feedback path from the macrocell can be used, which frees up the I/O pin for use as an input.

### **BLOCK DIAGRAM**

14127-001B

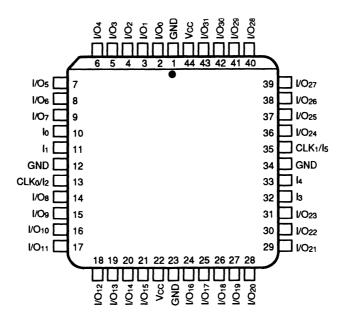

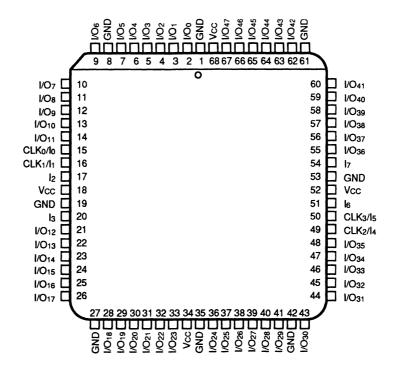

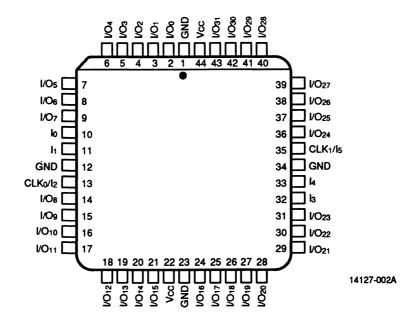

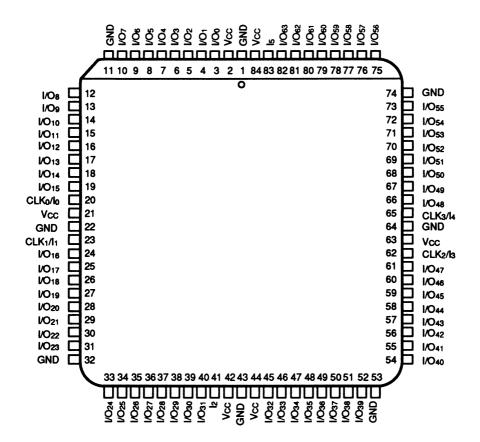

## CONNECTION DIAGRAM Top View

### PLCC/CQFP

### Pin Designations

CLK/I Clock or Input

GND Ground

Input

I/O Input/Output

Vcc Supply Voltage

14127-002A

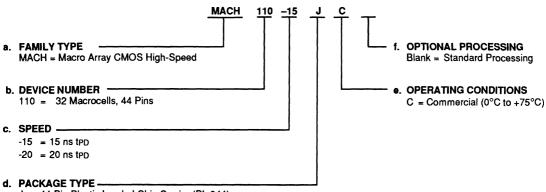

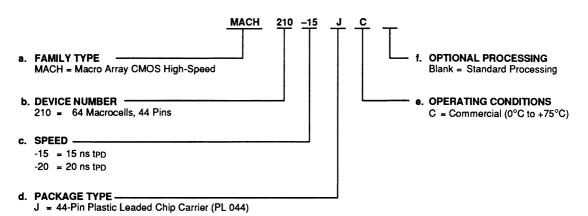

## **ORDERING INFORMATION Commercial Products**

AMD programmable logic products for commercial applications are available with several ordering options. The order number (Valid Combination) is formed by a combination of:

a. Family Type a. Family Type

b. Device Number

Speed C.

d. Package Type

e. Operating Conditions

f. Optional Processing

J = 44-Pin Plastic Leaded Chip Carrier (PL 044)

## **Valid Combinations**

MACH110-15JC MACH110-20JC

#### **Valid Combinations**

The Valid Combinations table lists configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check on newly released combinations.

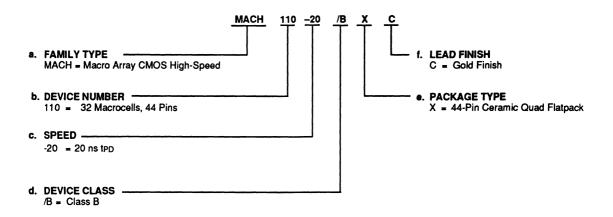

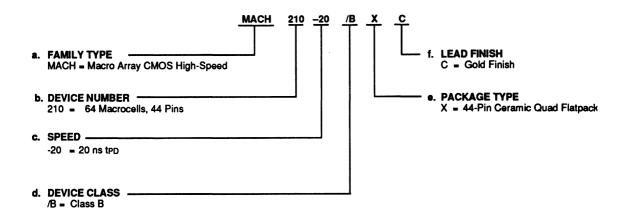

## **ORDERING INFORMATION (Preliminary) APL Products**

AMD programmable logic products for Aerospace and Defense applications are available with several ordering options. APL (Approved Product List) products are fully compliant with MIL-STD-883 requirements. The order number (Valid Combination) is formed by a combination of:

a. Family Type

b. Device Number

- Speed

- d. **Device Class**

- Package Type Lead Finish

**Valid Combinations** MACH110-20/BXC

#### **Valid Combinations**

The Valid Combinations table lists configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

#### **FUNCTIONAL DESCRIPTION**

The MACH110 consists of two PAL blocks connected by a switch matrix. There are 32 I/O pins and 6 dedicated input pins feeding the switch matrix. These signals are distributed to the two PAL blocks for efficient design implementation. There are two clock pins that can also be used as dedicated inputs.

#### The PAL Blocks

Each PAL block in the MACH110 (figure 8) contains a 64-product-term logic array, a logic allocator, 16 macrocells and 16 I/O cells. The switch matrix feeds each PAL block with 22 inputs. This makes the PAL block look effectively like an independent "PAL22V16".

There are four additional output enable product terms in each PAL block. For purposes of output enable, the 16 I/O cells are divided into 2 banks of 8 macrocells. Each bank is allocated two of the three-state product terms.

An asynchronous reset product term and an asynchronous preset product term are provided for flip-flop initialization. All flip-flops within the PAL block are initialized together.

#### The Switch Matrix

The MACH110 switch matrix is fed by the 6 dedicated inputs and all of the feedback signals from the PAL blocks. Each PAL block provides 16 internal feedback signals and 16 I/O feedback signals. The switch matrix distributes these signals back to the PAL blocks in an efficient manner that also provides for high performance. The design software automatically configures the switch matrix when fitting a design into the device.

#### The Product-Term Array

The MACH110 product-term array consists of 64 product terms for logic use, and 6 special-purpose product terms. Four of the special-purpose product terms provide programmable output enable, one provides asynchronous reset, and one provides asynchronous preset.

Two of the three-state product terms are used for the first eight I/O cells; the other two control the last eight macrocells.

#### The Logic Allocator

The logic allocator in the MACH110 takes the 64 logic product terms and allocates them to the 16 macrocells as needed. Each macrocell can be driven by up to 12 product terms. The design software automatically configures the logic allocator when fitting the design into the device.

#### The Macrocell

The MACH110 macrocells can be configured as either registered or combinatorial, with programmable polarity. The macrocell provides internal feedback whether configured as registered or combinatorial. The flip-flops can be configured as D-type or T-type, allowing for product-term optimization.

The flip-flops can individually select one of two clock pins, which are also available as data inputs. The registers are clocked on the LOW-to-HIGH transition of the clock signal. The flip-flops can also be asynchronously initialized with the common asynchronous reset and preset product terms.

#### The I/O Cell

The I/O cell in the MACH110 consists of a three-state output buffer. The three-state buffer can be configured in one of three ways: always enabled, always disabled, or controlled by a product term. If product term control is chosen, one of two product terms may be used to provide the control. The two product terms that are available are common to eight I/O cells.

These choices make it possible to use the macrocell as an output, an input, a bidirectional pin, or a three-state output for use in driving a bus.

Figure 8. MACH110 PAL Block

#### **ABSOLUTE MAXIMUM RATINGS**

Storage Temperature -65°C to +150°C

**Ambient Temperature**

with Power Applied -55°C to +125°C

Supply Voltage with

Respect to Ground -0.5 V to +7.0 V

DC Input Voltage -0.5 V to Vcc + 0.5 V

DC Output or I/O Pin Voltage -0.5 V to Vcc + 0.5 V

Static Discharge Voltage

Latchup Current

$(T_A = 0^{\circ}C \text{ to } 75^{\circ}C)$  200 mA

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability. Programming conditions may differ.

### **OPERATING RANGES**

Commercial (C) Devices

Temperature (T<sub>A</sub>) Operating

in Free Air 0°C to +75°C

Supply Voltage (Vcc) with

Respect to Ground +4.75 V to +5.25 V

Operating ranges define those limits between which the functionality of the device is guaranteed.

## DC CHARACTERISTICS over COMMERCIAL operating ranges unless otherwise specified

2001 V

| Parameter<br>Symbol | Parameter Description                    | Test Conditions                                                                                           | Min. | Max. | Unit     |

|---------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------|------|------|----------|

| Vон                 | Output HIGH Voltage                      | I <sub>OH</sub> = -3.2 mA, V <sub>CC</sub> = Min.<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | 2.4  |      | >        |

| Vol                 | Output LOW Voltage                       | IoL = 16 mA, Vcc = Min.<br>Vin = ViH or ViL                                                               |      | 0.5  | <b>V</b> |

| ViH                 | Input HIGH Voltage                       | Guaranteed Input Logical HIGH Voltage for all Inputs (Note 1)                                             | 2.0  |      | <b>V</b> |

| VIL                 | Input LOW Voltage                        | Guaranteed Input Logical LOW Voltage for all Inputs (Note 1)                                              |      | 8.0  | V        |

| Іін                 | Input HIGH Leakage Current               | V <sub>IN</sub> = 5.25 V, V <sub>CC</sub> = Max. (Note 2)                                                 |      | 10   | μА       |

| lıL                 | Input LOW Leakage Current                | Vin = 0 V, Vcc = Max. (Note 2)                                                                            |      | -10  | μΑ       |

| Іохн                | Off-State Output Leakage<br>Current HIGH | Vout = 5.25 V, Vcc = Max.<br>Vin = Vih or Vil (Note 2)                                                    |      | 10   | μΑ       |

| lozL                | Off-State Output Leakage<br>Current LOW  | Vout = 0 V, Vcc = Max.<br>Vin = Vih or Vil (Note 2)                                                       |      | -10  | μА       |

| Isc                 | Output Short-Circuit Current             | Vout = 0.5 V, Vcc = Max. (Note 3)                                                                         | -30  | -160 | mA       |

| lcc                 | Supply Current                           | VIN = 0 V, Outputs Open (Iout = 0 mA)<br>VCC = Max., f = 0 MHz                                            |      | 150  | mA       |

- 1. These are absolute values with respect to device ground and all overshoots due to system or tester noise are included.

- 2. I/O pin leakage is the worst case of IIL and IOZL (or IIH and IOZH).

- 3. Not more than one output should be shorted at a time and duration of the short-circuit should not exceed one second.

Vout = 0.5 V has been chosen to avoid test problems caused by tester ground degradation.

## **CAPACITANCE** (Note 1)

| Parameter<br>Symbol | Parameter Description | Test Conditions                                                     | Тур.  | Unit |

|---------------------|-----------------------|---------------------------------------------------------------------|-------|------|

| Cin                 | Input Capacitance     | V <sub>IN</sub> = 2.0 V V <sub>CC</sub> = 5.0 V, T <sub>A</sub> = 2 | 5°C 6 | pF   |

| Соит                | Output Capacitance    | Vout = 2.0 V f = 1 MHz                                              | 8     | pF   |

#### Note:

## **SWITCHING CHARACTERISTICS over COMMERCIAL operating ranges (Note 2)**

| Parameter |                                |                                                    |                                |          | -    | 15   | -2   | 0    |      |

|-----------|--------------------------------|----------------------------------------------------|--------------------------------|----------|------|------|------|------|------|

| Symbol    | Parameter D                    | escription                                         |                                |          | Min. | Max. | Min. | Max. | Unit |

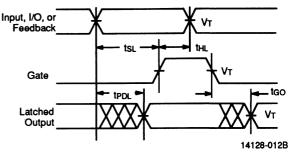

| tpp       | Input, I/O, or<br>Output (Note | Feedback to Combir<br>3)                           | natorial                       |          |      | 15   |      | 20   | ns   |

| •-        | Setup Time fr                  | om Input, I/O, or Fe                               | edback                         | D-type   | 10   |      | 13   |      | ns   |

| ts        | to Clock                       | •                                                  |                                | T-type   | 12   |      | 15   |      | ns   |

| tн        | Hold Time                      |                                                    |                                |          | 0    |      | 0    |      | ns   |

| tco       | Clock to Outp                  | out (Note 3)                                       |                                |          |      | 10   |      | 12   | ns   |

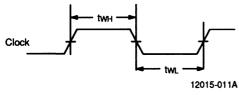

| tw.       | Clock Width                    |                                                    |                                | LOW      | 6    |      | 8    |      | ns   |

| twн       |                                |                                                    | <u> </u>                       |          |      |      | 8    |      | ns   |

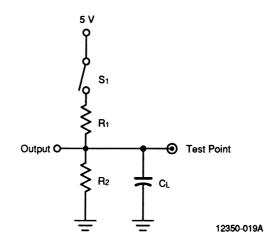

|           | Maximum Frequency              | I                                                  | D-type                         | 50       |      | 40   | i    | MHz  |      |

|           |                                | External Feedback                                  | external Feedback 1/(ts + tco) | T-type   | 45.5 |      | 37   |      | MHz  |

| fmax      |                                | Internal Feedback                                  |                                | D-type   | 66.6 |      | 47.6 |      | MHz  |

|           | (Note 4)                       | Internal Feedback                                  |                                | T-type   | 55.5 |      | 43.5 |      | MHz  |

|           |                                | No Feedback                                        | 1/(twL + twH                   | )        | 83.3 |      | 62.5 |      | MHz  |

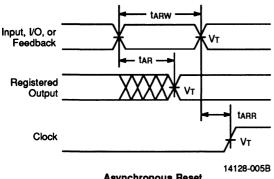

| tar       | Asynchronous                   | s Reset to Registere                               | d Output                       |          |      | 20   |      | 25   | ns   |

| tarw      | Asynchronous                   | s Reset Width (Note                                | 4)                             |          | 15   |      | 20   |      | ns   |

| tarr      | Asynchronous                   | s Reset Recovery Ti                                | me (Note 4)                    |          | 10   |      | 15   |      | ns   |

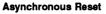

| tap       | Asynchronous                   | s Preset to Registere                              | ed Output                      |          |      | 20   |      | 25   | ns   |

| tapw      | Asynchronous                   | s Preset Width (Note                               | Preset Width (Note 4)          |          |      |      | 20   |      | ns   |

| tapr      | Asynchronous                   | chronous Preset Recovery Time (Note 4)             |                                |          | 10   |      | 15   |      | ns   |

| tea .     | Input, I/O, or I               | ut, I/O, or Feedback to Output Enable (Notes 3, 4) |                                |          |      | 15   |      | 20   | ns   |

| ten       | Input, I/O, or I               | Feedback to Output                                 | Disable (Not                   | es 3, 4) |      | 15   |      | 20   | ns   |

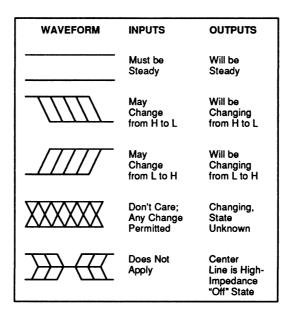

- 2. See Switching Test Circuit, page 69, for test conditions.

- 3. Parameters measured with 16 outputs switching.

- 4. These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where frequency may be affected.

These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where capacitance may be affected.

#### **ABSOLUTE MAXIMUM RATINGS**

Storage Temperature -65°C to +150°C

**Ambient Temperature**

with Power Applied -55°C to +125°C

Supply Voltage with

Respect to Ground -0.5 V to +7.0 V

DC Input Voltage -0.5 V to Vcc + 0.5 V

DC Output or I/O

Pin Voltage -0.5 V to Vcc + 0.5 V

Static Discharge Voltage 2001 V

Latchup Current

$(T_C = -55^{\circ}C \text{ to } +125^{\circ}C)$  200 mA

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability. Programming conditions may differ. Absolute Maximum Ratings are for system design reference; parameters given are not tested.

#### **OPERATING RANGES**

Military (M) Devices (Note 1)

Operating Case

Temperature (Tc) -55°C to +125°C

Supply Voltage (Vcc)

with Respect to Ground +4.5 V to +5.5 V

Operating ranges define those limits between which the functionality of the device is guaranteed.

#### Note:

Military products are tested at Tc = +25°C, +125°C and -55°C, per MIL-STD-883.

## DC CHARACTERISTICS over MILITARY operating ranges unless otherwise specified (Note 2)

|                     | PRELIMINARY                              |                                                                                        |      |      |      |  |  |  |  |

|---------------------|------------------------------------------|----------------------------------------------------------------------------------------|------|------|------|--|--|--|--|

| Parameter<br>Symbol | Parameter Description                    | Test Conditions                                                                        | Min. | Max. | Unit |  |  |  |  |

| Vон                 | Output HIGH Voltage                      | IOH = -2.0 mA, Vcc = Min.<br>VIN = VIH Or VIL                                          | 2.4  |      | ٧    |  |  |  |  |

| VoL                 | Output LOW Voltage                       | IoL = 12 mA, Vcc = Min.<br>Vin = Vih or Vil                                            |      | 0.5  | ٧    |  |  |  |  |

| ViH                 | Input HIGH Voltage                       | Guaranteed Input Logical HIGH<br>Voltage for all Inputs (Note 3)                       | 2.0  |      | ٧    |  |  |  |  |

| VIL                 | Input LOW Voltage                        | Guaranteed Input Logical LOW<br>Voltage for all Inputs (Note 3)                        |      | 0.8  | ٧    |  |  |  |  |

| lн                  | Input HIGH Leakage Current               | V <sub>IN</sub> = 5.5 V, V <sub>CC</sub> = Max. (Note 4)                               |      | 10   | μΑ   |  |  |  |  |

| lıL                 | Input LOW Leakage Current                | VIN = 0 V, Vcc = Max. (Note 4)                                                         |      | -10  | μΑ   |  |  |  |  |

| Іохн                | Off-State Output Leakage<br>Current HIGH | Vout = 5.5 V, Vcc = Max.<br>Vin = Vih or Vil (Note 4)                                  |      | 40   | μА   |  |  |  |  |

| lozl                | Off-State Output Leakage<br>Current LOW  | Vout = 0 V, Vcc = Max.<br>Vin = Vih or Vil (Note 4)                                    |      | -40  | μА   |  |  |  |  |

| Isc                 | Output Short-Circuit Current             | Vout = 0.5 V, Vcc = Max. (Note 5)                                                      | -30  | -200 | mA   |  |  |  |  |

| lcc                 | Supply Current                           | V <sub>IN</sub> = 0 V, Outputs Open (lout = 0 mA)<br>V <sub>CC</sub> = Max., f = 0 MHz |      | 200  | mA   |  |  |  |  |

- 2. For APL products, Group A, Subgroups 1, 2 and 3 are tested per MIL-STD-883, Method 5005, unless otherwise noted.

- 3. VIL and VIH are input conditions of output tests and are not themselves directly tested. VIL and VIH are absolute voltages with respect to device ground and include all overshoots due to system and/or tester noise. Do not attempt to test these values without suitable equipment.

- 4. I/O pin leakage is the worst case of IIL and IOZL (or IIH and IOZH).

- 5. Not more than one output should be shorted at a time and duration of the short-circuit should not exceed one second.

VOUT = 0.5 V has been chosen to avoid test problems caused by tester ground degradation. This parameter is not 100% tested, but is evaluated at initial characterization and at any time the design is modified where Isc may be affected.

### **CAPACITANCE (Note 1)**

| Parameter<br>Symbol | Parameter Description | Test Conditio | ns                     | Тур. | Unit |

|---------------------|-----------------------|---------------|------------------------|------|------|

| Cin                 | Input Capacitance     | VIN = 2.0 V   | Vcc = 5.0 V, Ta = 25°C | 8    | pF   |

| Соит                | Output Capacitance    | Vout = 2.0 V  | f = 1 MHz              | 9    | pF   |

#### Note:

### **SWITCHING CHARACTERISTICS over MILITARY operating ranges (Note 2)**

|                     |                        | P                                         | RELIMI        | NARY         | <del></del> |      |      |

|---------------------|------------------------|-------------------------------------------|---------------|--------------|-------------|------|------|

| Parameter<br>Symbol | - Borometer            | Description                               |               |              | Min.        | Max. | Unit |

| teo                 |                        | Description r Feedback to Comb            | inatorial Out | nut (Noto 3) | Will.       | 20   | ns   |

| IPD                 | <del></del>            |                                           |               | <u> </u>     | 13          | 20   | ns   |

| ts                  | Setup Time<br>to Clock |                                           |               | D-type       | 15          |      |      |

|                     |                        |                                           |               | T-type       |             |      | ns   |

| tH                  | Hold Time              |                                           |               |              | 0           |      | ns   |

| tco                 | Clock to Out           | tput (Note 3)                             |               |              |             | 12   | ns   |

| twL                 | Clock Width            |                                           |               | LOW          | 8           |      | ns   |

| twн                 | CIOCK WIGHT            |                                           |               | HIGH         | 8           |      | ns   |

|                     |                        |                                           | 4"            | D-type       | 40          |      | MHz  |

| Mavimu              | <br>  Maximum          | External Feedback                         | 1/(15 + 100)  | T-type       | 37          |      | MHz  |

| <b>fmax</b>         | Frequency              |                                           |               | D-type       | 47.6        |      | MHz  |

|                     | (Note 4)               | Internal Feedback                         |               | T-type       | 43.5        |      | MHz  |

|                     |                        | No Feedback                               | 1/(twL + tw-  | 1)           | 62.5        |      | MHz  |

| tar                 | Asynchrono             | us Reset to Register                      | ed Output     |              |             | 25   | ns   |

| tarw                | Asynchrono             | us Reset Width (Not                       | e 4)          |              | 20          |      | ns   |

| tarr                | Asynchrono             | us Reset Recovery                         | Time (Note 4  | )            | 15          |      | ns   |

| <b>t</b> AP         | Asynchrono             | us Preset to Registe                      | red Output    |              |             | 25   | ns   |

| tapw                | Asynchrono             | ous Preset Width (Note 4)                 |               |              | 20          |      | ns   |

| tapr                | Asynchrono             | Asynchronous Reset Recovery Time (Note 4) |               |              | 15          |      | ns   |

| tea .               | Input, I/O, o          | r Feedback to Outpu                       | t Enable (No  | otes 3, 4)   |             | 20   | ns   |

| ten                 | Input, I/O, or         | r Feedback to Outpu                       | t Disable (N  | otes 3, 4)   |             | 20   | ns   |

- 2. See Switching Test Circuit, page 69, for test conditions. For APL products, Group A, Subgroups 9, 10 and 11 are tested per MIL-STD-883, Method 5005, unless otherwise noted.

- 3. Parameters measured with 16 outputs switching.

- These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where these parameters may be affected.

These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where capacitance may be affected.

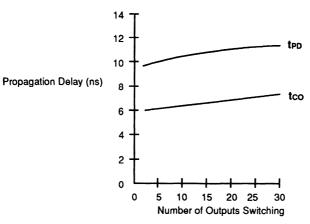

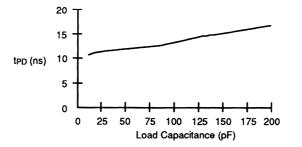

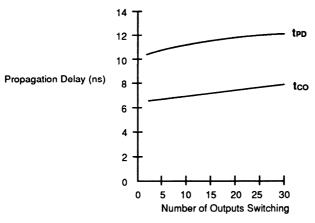

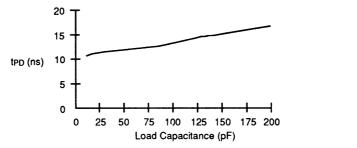

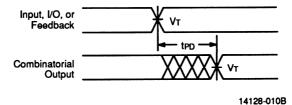

### **TYPICAL SWITCHING CHARACTERISTICS**

$V_{CC} = 5.0 \text{ V}, T_A = 25^{\circ}\text{C}$

tpp, tco vs Number of Outputs Switching

14127-005A

14127-006A

**tPD vs Load Capacitance**

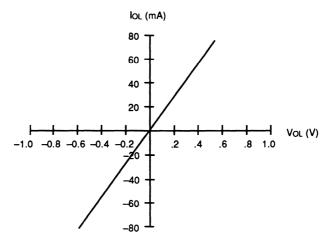

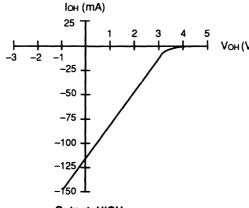

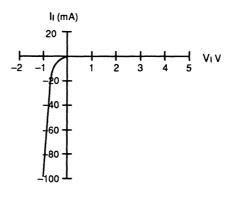

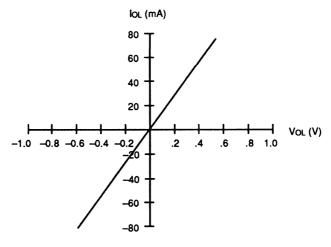

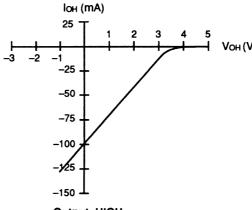

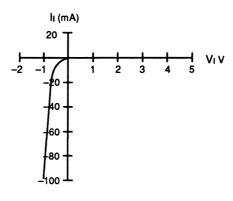

## TYPICAL CURRENT VS. VOLTAGE (I-V) CHARACTERISTICS

$Vcc = 5.0 \text{ V}, T_A = 25^{\circ}C$

**Output, LOW**

14127-007A

**Output, HIGH**

14127-008A

14127-009A

Input

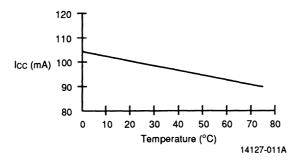

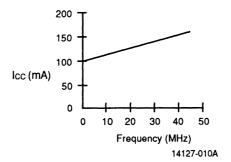

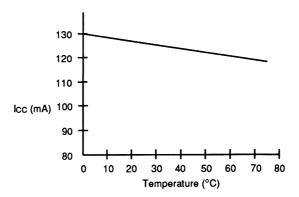

## TYPICAL Icc CHARACTERISTICS

$V_{CC} = 5.0 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ , frequency = 0 MHz unless otherwise specified

Icc vs. Operating Temperature

Icc vs. Operating Frequency

## Advanced Micro Devices

## MACH120-15/20

## **High-Density EE CMOS Programmable Logic**

#### **DISTINCTIVE CHARACTERISTICS**

- 68 Pins

- 48 Macrocells

- 15 ns tpD Commercial 20 ns tpD Military

- 50 MHz f<sub>MAX</sub> Commercial 40 MHz f<sub>MAX</sub> Military

- 56 Inputs

- **■** 48 Outputs

- 48 Flip-flops

- 4 PAL blocks

- Pin-compatible with MACH220

#### **GENERAL DESCRIPTION**

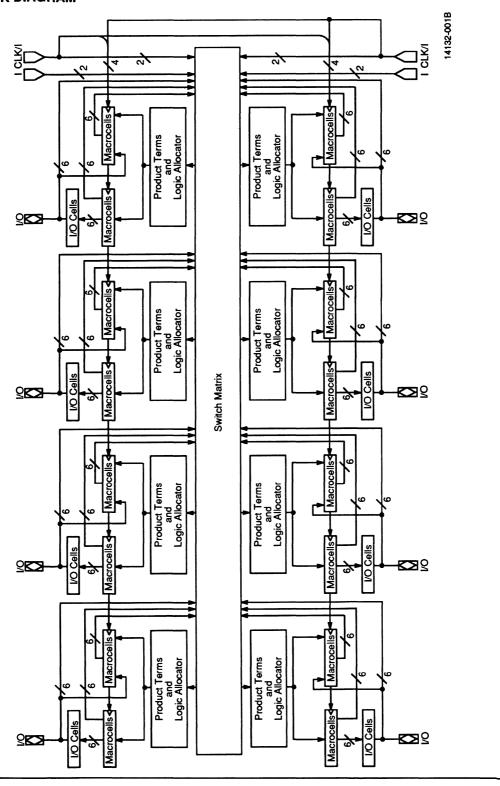

The MACH120 is a member of AMD's high-performance EE CMOS MACH 1 family. This device has approximately five times the logic macrocell capability of the popular PAL22V10 at an equal speed with a lower cost per macrocell.

The MACH120 consists of four PAL blocks interconnected by a programmable switch matrix. The switch matrix connects the PAL blocks to each other and to all input pins, providing a high degree of connectivity between the fully-connected PAL blocks. This allows designs to be placed and routed efficiently.

The MACH120 macrocell provides either registered or combinatorial outputs with programmable polarity. If a registered configuration is chosen, the register can be configured as D-type or T-type to help reduce the number of product terms. The register type decision can be made by the designer or by the software. All macrocells can be connected to an I/O cell. If a buried macrocell is desired, the internal feedback path from the macrocell can be used, which frees up the I/O pin for use as an input.

#### **BLOCK DIAGRAM**

Publication# 14129 Rev. C Amendment/0 Issue Date: April 1991

## CONNECTION DIAGRAMS Top View

#### **Pin Designations**

CLK/I Clock or Input

GND Ground

I Input

I/O Input/Output

Vcc Supply Voltage

#### **FUNCTIONAL DESCRIPTION**

The MACH120 consists of four PAL blocks connected by a switch matrix. There are 48 I/O pins and 4 dedicated input pins feeding the switch matrix. These signals are distributed to the four PAL blocks for efficient design implementation. There are 4 clock pins that can also be used as dedicated inputs.

#### The PAL Blocks

Each PAL block in the MACH120 (figure 9) contains a 48-product-term logic array, a logic allocator, 12 macrocells and 12 I/O cells. The switch matrix feeds each PAL block with 26 inputs. This makes the PAL block look effectively like an independent "PAL26V12".

There are four additional output enable product terms in each PAL block. For purposes of output enable, the 12 I/O cells are divided into 2 banks of 6 macrocells. Each bank is allocated two of the three-state product terms.

An asynchronous reset product term and an asynchronous preset product term are provided for flip-flop initialization. All flip-flops within the PAL block are initialized together.

#### The Switch Matrix

The MACH120 switch matrix is fed by the 8 dedicated inputs and all of the feedback signals from the PAL blocks. Each PAL block provides 12 internal feedback signals and 12 I/O feedback signals. The switch matrix distributes these signals back to the PAL blocks in an efficient manner that also provides for high performance. The design software automatically configures the switch matrix when fitting a design into the device.

#### The Product-Term Array

The MACH120 product-term array consists of 48 product terms for logic use, and 6 special-purpose product terms. Four of the special-purpose product terms provide programmable output enable, one provides asynchronous reset, and one provides asynchronous preset.

Two of the three-state product terms are used for the first six I/O cells; the other two control the last six macrocells.

#### The Logic Allocator

The logic allocator in the MACH120 takes the 48 logic product terms and allocates them to the 12 macrocells as needed. Each macrocell can be driven by up to 12 product terms. The design software automatically configures the logic allocator when fitting the design into the device.

#### The Macrocell

The MACH120 macrocells can be configured as either registered or combinatorial, with programmable polarity. The macrocell provides internal feedback whether configured as registered or combinatorial. The flip-flops can be configured as D-type or T-type, allowing for product-term optimization.

The flip-flops can individually select one of four global clock pins, which are also available as logic inputs. The registers are clocked on the LOW-to-HIGH transition of the clock signal. The flip-flops can also be asynchronously initialized with the common asynchronous reset and preset product terms.

#### The I/O Cell

The I/O cell in the MACH120 consists of a three-state output buffer. The three-state buffer can be configured in one of three ways: always enabled, always disabled, or controlled by a product term. If product term control is chosen, one of two product terms may be used to provide the control. The two product terms that are available are common to six I/O cells.

These choices make it possible to use the macrocell as an output, an input, a bidirectional pin, or a three-state output for use in driving a bus.

Figure 9. MACH120 PAL Block

**ABSOLUTE MAXIMUM RATINGS**

Storage Temperature -65°C to +150°C

**Ambient Temperature**

with Power Applied -55°C to +125°C

Supply Voltage with

Respect to Ground -0.5 V to +7.0 V

DC Input Voltage -0.5 V to Vcc + 0.5 V

DC Output or I/O Pin Voltage -0.5 V to Vcc + 0.5 V

Static Discharge Voltage 2001 V

**Latchup Current**

$(T_A = 0^{\circ}C \text{ to } 75^{\circ}C)$  200 mA

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability. Programming conditions may differ.

### **OPERATING RANGES**

Commercial (C) Devices

Temperature (T<sub>A</sub>) Operating

in Free Air 0°C to +75°C

Supply Voltage (Vcc) with

Respect to Ground +4.75 V to +5.25 V

Operating ranges define those limits between which the functionality of the device is guaranteed.

## DC CHARACTERISTICS over COMMERCIAL operating ranges unless otherwise specified

|                     | Р                                        | RELIMINARY                                                                             |      |      |      |

|---------------------|------------------------------------------|----------------------------------------------------------------------------------------|------|------|------|

| Parameter<br>Symbol | Parameter Description                    | Test Conditions                                                                        | Min. | Max. | Unit |

| Vон                 | Output HIGH Voltage                      | IOH = -3.2 mA, Vcc = Min.<br>VIN = VIH Or VIL                                          | 2.4  |      | ٧    |

| Vol                 | Output LOW Voltage                       | IOL = 16 mA, Vcc = Min.<br>VIN = VIH Or VIL                                            |      | 0.5  | ٧    |

| ViH                 | Input HIGH Voltage                       | Guaranteed Input Logical HIGH<br>Voltage for all Inputs (Note 1)                       | 2.0  |      | ٧    |

| ViL                 | Input LOW Voltage                        | Guaranteed Input Logical LOW Voltage for all Inputs (Note 1)                           |      | 0.8  | ٧    |

| lıн                 | Input HIGH Leakage Current               | V <sub>IN</sub> = 5.25 V, V <sub>CC</sub> = Max. (Note 2)                              |      | 10   | μА   |

| İIL                 | Input LOW Leakage Current                | V <sub>IN</sub> = 0 V, V <sub>CC</sub> = Max. (Note 2)                                 |      | -10  | μΑ   |

| Іохн                | Off-State Output Leakage<br>Current HIGH | Vout = 5.25 V, Vcc = Max.<br>Vin = Vih or Vil (Note 2)                                 |      | 10   | μА   |

| lozl                | Off-State Output Leakage<br>Current LOW  | Vout = 0 V, Vcc = Max.<br>Vin = Vih or Vil (Note 2)                                    |      | -10  | μА   |

| Isc                 | Output Short-Circuit Current             | Vout = 0.5 V, Vcc = Max. (Note 3)                                                      | -30  | -130 | mA   |

| lcc                 | Supply Current                           | V <sub>IN</sub> = 0 V, Outputs Open (Iout = 0 mA)<br>V <sub>CC</sub> = Max., f = 0 MHz |      | 180  | mA   |

- 1. These are absolute values with respect to device ground and all overshoots due to system or tester noise are included.

- 2. I/O pin leakage is the worst case of IIL and IOZL (or IIH and IOZH).

- Not more than one output should be shorted at a time and duration of the short-circuit should not exceed one second.

Vout = 0.5 V has been chosen to avoid test problems caused by tester ground degradation.

## **CAPACITANCE (Note 1)**

| Parameter<br>Symbol | Parameter Description | Test Condition          | ons                                | Тур. | Unit |

|---------------------|-----------------------|-------------------------|------------------------------------|------|------|

| Cin                 | Input Capacitance     | V <sub>IN</sub> = 2.0 V | Vcc = 5.0 V, T <sub>A</sub> = 25°C |      | рF   |

| Соит                | Output Capacitance    | Vout = 2.0 V            | f = 1 MHz                          |      | pF   |

#### Note:

## **SWITCHING CHARACTERISTICS over COMMERCIAL operating ranges (Note 2)**

|           |                                            | P                              | RELIMI       | NARY     |      |      |      |      |      |

|-----------|--------------------------------------------|--------------------------------|--------------|----------|------|------|------|------|------|

| Parameter |                                            |                                |              |          | -18  | 5    | -20  | )    |      |

| Symbol    | Parameter D                                | escription                     |              |          | Min. | Max. | Min. | Max. | Unit |

| tpD       | Input, I/O, or                             | Feedback to Combin             | atorial      |          |      | 15   |      | 20   | ns   |

|           | Output (Note                               | 3)                             |              |          |      |      |      |      |      |

| •-        | Setup Time                                 | from Input, I/O, or F          | eedback      | D-type   | 10   |      |      | 13   | ns   |

| ts        | to Clock                                   |                                |              | T-type   | 12   |      | 15   |      | ns   |

| tн        | Hold Time                                  |                                |              |          | 0    |      | 0    |      | ns   |

| tco       | Clock to Outp                              | out (Note 3)                   |              |          |      | 10   |      | 12   | ns   |

| twL       | Clock Width                                |                                |              | LOW      | 6    |      | 8    |      | ns   |

| twн       | Clock width                                | 1                              |              | HIGH     | 6    |      | 8    |      | ns   |

|           |                                            |                                |              | D-type   | 50   |      | 40   |      | MHz  |

|           | Maximum                                    | External Feedback              | 1/(ts + tco) | T-type   | 45.5 |      | 37   |      | MHz  |

| fmax      | Frequency                                  |                                |              | D-type   | 66.6 |      | 47.6 |      | MHz  |

|           | (Note 4)                                   | Internal Feedback              |              | T-type   | 55.5 |      | 43.5 |      | MHz  |

|           |                                            | No Feedback                    | 1/(twL + tw- | 1)       | 83.3 |      | 62.5 |      | MHz  |

| tar       | Asynchronou                                | s Reset to Registere           | d Output     |          |      | 20   |      | 25   | ns   |

| tarw      | Asynchronou                                | s Reset Width (Note            | 4)           |          | 15   |      | 20   |      | ns   |

| tarr      | Asynchronou                                | s Reset Recovery Ti            | me (Note 4)  |          | 10   |      | 15   |      | ns   |

| tap       | Asynchronou                                | us Preset to Registered Output |              |          |      | 20   |      | 25   | ns   |

| tapw      | Asynchronou                                | onous Preset Width (Note 4)    |              |          | 15   |      | 20   |      | ns   |

| tapr      | Asynchronous Preset Recovery Time (Note 4) |                                |              | 10       |      | 15   |      | ns   |      |

| tea       | Input, I/O, or                             | Feedback to Output             | Enable (Note | es 3, 4) |      | 15   |      | 20   | ns   |

| ter       | Input, I/O, or                             | Feedback to Output             | Disable (Not | es 3, 4) |      | 15   |      | 20   | ns   |

- 2. See Switching Test Circuit, page 69, for test conditions.

- 3. Parameters measured with 24 outputs switching.

- These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where frequency may be affected.

These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where capacitance may be affected.

## Advanced Micro Devices

## MACH130-15/20

## **High-Density EE CMOS Programmable Logic**

#### **DISTINCTIVE CHARACTERISTICS**

- 84 Pins

- 64 Macrocells

- 15 ns tpD Commercial 20 ns tpD Military

- 50 MHz fMAX Commercial 40 MHz fMAX Military

- 70 Inputs

- 64 Outputs

- 64 Flip-flops

- 4 "PAL26V16" Blocks with buried Macrocells

- Pin-compatible with MACH230

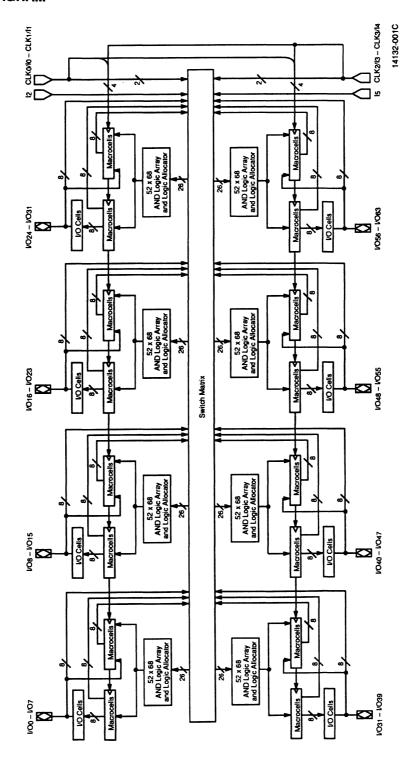

#### **GENERAL DESCRIPTION**

The MACH130 is a member of AMD's high-performance EE CMOS MACH 1 family. This device has approximately six times the logic macrocell capability of the popular PAL22V10 at an equal speed with a lower cost per macrocell.

The MACH130 consists of four PAL blocks interconnected by a programmable switch matrix. The switch matrix connects the PAL blocks to each other and to all input pins, providing a high degree of connectivity between the fully-connected PAL blocks. This allows designs to be placed and routed efficiently.

The MACH130 macrocell provides either registered or combinatorial outputs with programmable polarity. If a registered configuration is chosen, the register can be configured as D-type or T-type to help reduce the number of product terms. The register type decision can be made by the designer or by the software. All macrocells can be connected to an I/O cell. If a buried macrocell is desired, the internal feedback path from the macrocell can be used, which frees up the I/O pin for use as an input.

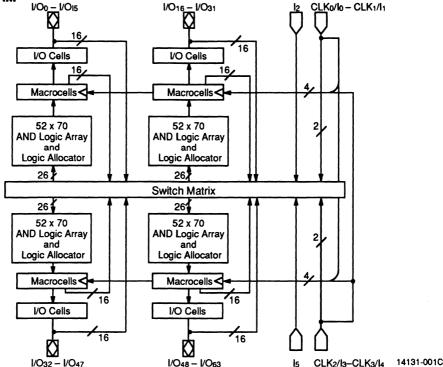

#### **BLOCK DIAGRAM**

Publication # 14131 Rev. C Amendment/0 Issue Date: April 1991

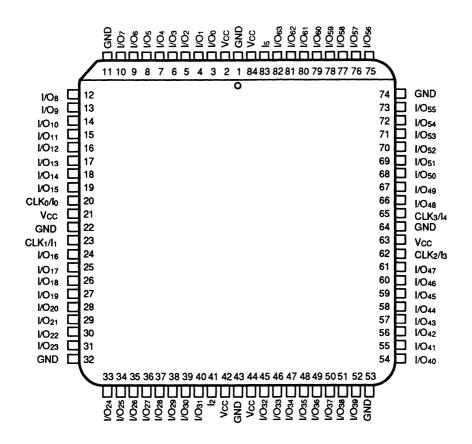

## CONNECTION DIAGRAM Top View

#### PLCC/CQFP

#### Pin Designations

CLK/I Clock or Input

GND Ground

I Input

I/O Input/Output

Vcc Supply Voltage

### **FUNCTIONAL DESCRIPTION**

The MACH130 consists of four PAL blocks connected by a switch matrix. There are 64 I/O pins and 2 dedicated input pins feeding the switch matrix. These signals are distributed to the four PAL blocks for efficient design implementation. There are 4 clock pins that can also be used as dedicated inputs.

#### The PAL Blocks

Each PAL block in the MACH130 (figure 10) contains a 64-product-term logic array, a logic allocator, 16 macrocells and 16 I/O cells. The switch matrix feeds each PAL block with 26 inputs. This makes the PAL block look effectively like an independent "PAL26V16".

There are four additional output enable product terms in each PAL block. For purposes of output enable, the 16 I/O cells are divided into 2 banks of 8 macrocells. Each bank is allocated two of the three-state product terms.

An asynchronous reset product term and an asynchronous preset product term are provided for flip-flop initialization. All flip-flops within the PAL block are initialized together.

#### The Switch Matrix

The MACH130 switch matrix is fed by the 6 dedicated inputs and all of the feedback signals from the PAL blocks. Each PAL block provides 16 internal feedback signals and 16 I/O feedback signals. The switch matrix distributes these signals back to the PAL blocks in an efficient manner that also provides for high performance. The design software automatically configures the switch matrix when fitting a design into the device.

## The Product-Term Array

The MACH130 product-term array consists of 64 product terms for logic use, and 6 special-purpose product terms. Four of the special-purpose product terms provide programmable output enable, one provides asynchronous reset, and one provides asynchronous preset.

Two of the three-state product terms are used for the first eight I/O cells; the other two control the last eight macrocells.

## The Logic Allocator

The logic allocator in the MACH130 takes the 64 logic product terms and allocates them to the 16 macrocells as needed. Each macrocell can be driven by up to 12 product terms. The design software automatically configures the logic allocator when fitting the design into the device.

#### The Macrocell

The MACH130 macrocells can be configured as either registered or combinatorial, with programmable polarity. The macrocell provides internal feedback whether configured as registered or combinatorial. The flip-flops can be configured as D-type or T-type, allowing for product-term optimization.

The flip-flops can individually select one of four global clock pins, which are also available as logic inputs. The registers are clocked on the LOW-to-HIGH transition of the clock signal. The flip-flops can also be asynchronously initialized with the common asynchronous reset and preset product terms.

#### The I/O Cell

The I/O cell in the MACH130 consists of a three-state output buffer. The three-state buffer can be configured in one of three ways: always enabled, always disabled, or controlled by a product term. If product term control is chosen, one of two product terms may be used to provide the control. The two product terms that are available are common to eight I/O cells.

These choices make it possible to use the macrocell as an output, an input, a bidirectional pin, or a three-state output for use in driving a bus.

Figure 10. MACH130 PAL Block

**ABSOLUTE MAXIMUM RATINGS**

Storage Temperature -65°C to +150°C

**Ambient Temperature**

with Power Applied -55°C to +125°C

Supply Voltage with

Respect to Ground -0.5 V to +7.0 V

DC Input Voltage -0.5 V to Vcc + 0.5 V

DC Output or I/O Pin Voltage -0.5 V to Vcc + 0.5 V

Static Discharge Voltage 2001 V

**Latchup Current**

$(T_A = 0^{\circ}C \text{ to } 75^{\circ}C)$  200 mA

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability. Programming conditions may differ.

## **OPERATING RANGES**

Commercial (C) Devices

Temperature (T<sub>A</sub>) Operating

in Free Air 0°C to +75°C

Supply Voltage (Vcc) with

Respect to Ground +4.75 V to +5.25 V

Operating ranges define those limits between which the functionality of the device is guaranteed.

## DC CHARACTERISTICS over COMMERCIAL operating ranges unless otherwise specified

|                     | Р                                        | RELIMINARY                                                                             |      |      |      |

|---------------------|------------------------------------------|----------------------------------------------------------------------------------------|------|------|------|

| Parameter<br>Symbol | Parameter Description                    | Test Conditions                                                                        | Min. | Max. | Unit |

| Vон                 | Output HIGH Voltage                      | IOH = -3.2 mA, Vcc = Min.<br>VIN = VIH Or VIL                                          | 2.4  |      | ٧    |

| Vol                 | Output LOW Voltage                       | IoL = 16 mA, Vcc = Min.<br>Vin = Vih or Vil                                            |      | 0.5  | ٧    |

| ViH                 | Input HIGH Voltage                       | Guaranteed Input Logical HIGH<br>Voltage for all Inputs (Note 1)                       | 2.0  |      | ٧    |

| VIL                 | Input LOW Voltage                        | Guaranteed Input Logical LOW Voltage for all Inputs (Note 1)                           |      | 0.8  | ٧    |

| lін                 | Input HIGH Leakage Current               | V <sub>IN</sub> = 5.25 V, V <sub>CC</sub> = Max. (Note 2)                              |      | 10   | μА   |

| lıL.                | Input LOW Leakage Current                | VIN = 0 V, Vcc = Max. (Note 2)                                                         |      | -10  | μΑ   |

| Іохн                | Off-State Output Leakage<br>Current HIGH | Vout = 5.25 V, Vcc = Max.<br>Vin = Vih or Vil (Note 2)                                 |      | 10   | μА   |

| lozl                | Off-State Output Leakage<br>Current LOW  | Vout = 0 V, Vcc = Max.<br>Vin = Vih or Vil (Note 2)                                    |      | -10  | μΑ   |

| Isc                 | Output Short-Circuit Current             | Vout = 0.5 V, Vcc = Max. (Note 3)                                                      | -30  | -130 | mA   |

| lcc                 | Supply Current                           | V <sub>IN</sub> = 0 V, Outputs Open (lout = 0 mA)<br>V <sub>CC</sub> = Max., f = 0 MHz |      | 180  | mA   |

- 1. These are absolute values with respect to device ground and all overshoots due to system or tester noise are included.

- 2. I/O pin leakage is the worst case of IIL and IOZL (or IIH and IOZH).

- 3. Not more than one output should be shorted at a time and duration of the short-circuit should not exceed one second.

Vout = 0.5 V has been chosen to avoid test problems caused by tester ground degradation.

## **CAPACITANCE** (Note 1)

| Parameter<br>Symbol | Parameter Description | Test Condition | Test Conditions                    |  | Unit |

|---------------------|-----------------------|----------------|------------------------------------|--|------|

| Cin                 | Input Capacitance     | VIN = 2.0 V    | Vcc = 5.0 V, T <sub>A</sub> = 25°C |  | pF   |

| Соит                | Output Capacitance    | Vout = 2.0 V   | f = 1 MHz                          |  | pF   |

#### Note:

1. These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where capacitance may be affected.

## **SWITCHING CHARACTERISTICS over COMMERCIAL operating ranges (Note 2)**

|           |                                            | Р                                      | RELIMI       | NARY     |      |      |      |      |      |

|-----------|--------------------------------------------|----------------------------------------|--------------|----------|------|------|------|------|------|

| Parameter |                                            |                                        |              |          | -1   | 5    | -2   | 0    |      |

| Symbol    | Parameter D                                | escription                             |              |          | Min. | Max. | Min. | Max. | Unit |

| tpD       | Input, I/O, or                             | put, I/O, or Feedback to Combinatorial |              |          |      | 15   |      | 20   | ns   |

|           | Output (Note                               | 3)                                     |              |          |      |      |      |      |      |

| A-        | Setup Time from Input, I/O, or Feedback    |                                        |              | D-type   | 10   |      |      | 13   | ns   |

| ts        | to Clock                                   |                                        |              | T-type   | 12   |      | 15   |      | ns   |

| tн        | Hold Time                                  |                                        |              |          | 0    |      | 0    |      | ns   |

| tco       | Clock to Outp                              | Clock to Output (Note 3)               |              |          |      | 10   |      | - 12 | ns   |

| tw∟       | Clock Width                                | Clock Width                            |              |          | 6    |      | 8    |      | ns   |

| twн       | CIOCK WIGHT                                |                                        |              |          | 6    |      | 8    |      | ns   |

|           |                                            |                                        | D-type       | 50       |      | 40   |      | MHz  |      |

|           | Maximum                                    | External Feedback                      | 1/(15 + 100) | T-type   | 45.5 |      | 37   |      | MHz  |

| fmax      | Frequency                                  | requency                               | <b>.</b>     | D-type   | 66.6 |      | 47.6 |      | MHz  |

|           | (Note 4)                                   |                                        |              | T-type   | 55.5 |      | 43.5 |      | MHz  |

|           |                                            | No Feedback                            | 1/(twL + twi | 1)       | 83.3 |      | 62.5 |      | MHz  |

| tar       | Asynchronou                                | s Reset to Registered                  | d Output     |          |      | 20   |      | 25   | ns   |

| tarw      | Asynchronou                                | s Reset Width (Note                    | 4)           |          | 15   |      | 20   |      | ns   |